# **Axcelerator Family FPGAs**

### Leading-Edge Performance

- 350+ MHz System Performance

- 500+ MHz Internal Performance

- High-Performance Embedded FIFOs

- 700 Mb/s LVDS Capable I/Os

#### **Specifications**

- Up to 2 Million Equivalent System Gates

- Up to 684 I/Os

- Up to 10,752 Dedicated Flip-Flops

- Up to 295 kbits Embedded SRAM/FIFO

- Manufactured on Advanced 0.15 μm CMOS Antifuse Process Technology, 7 Layers of Metal

#### **Features**

- Single-Chip, Nonvolatile Solution

- Up to 100% Resource Utilization with 100% Pin Locking

- 1.5V Core Voltage for Low Power

- Footprint Compatible Packaging

- Flexible, Multi-Standard I/Os:

- 1.5V, 1.8V, 2.5V, 3.3V Mixed Voltage Operation

- Bank-Selectable I/Os 8 Banks per Chip

- Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3V PCI, and 3.3V PCI-X

- Differential I/O Standards: LVPECL and LVDS

#### Table 1-1 • Axcelerator Family Product Profile

- Voltage-Referenced I/O Standards: GTL+, HSTL Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

Registered I/Os

- Hot-Swap Compliant I/Os (except PCI)

- Programmable Slew Rate and Drive Strength on Outputs

- Programmable Delay and Weak Pull-Up/Pull-Down Circuits on Inputs

- Embedded Memory:

- Variable-Aspect 4,608-bit RAM Blocks (x1, x2, x4, x9, x18, x36 Organizations Available)

- Independent, Width-Configurable Read and Write Ports

Programmable Embedded FIFO Control Logic

- Segmentable Clock Resources

- Embedded Phase-Locked Loop:

- 14-200 MHz Input Range

- Frequency Synthesis Capabilities up to 1 GHz

- Deterministic, User-Controllable Timing

- Unique In-System Diagnostic and Debug Capability

with Actel Silicon Explorer II

- Boundary-Scan Testing Compliant with IEEE Standard 1149.1 (JTAG)

- FuseLock<sup>TM</sup> Secure Programming Technology Prevents Reverse Engineering and Design Theft

| Device                                | AX125    | AX250    | AX500    | AX1000        | AX2000    |

|---------------------------------------|----------|----------|----------|---------------|-----------|

| Capacity (in Equivalent System Gates) | 125,000  | 250,000  | 500,000  | 1,000,000     | 2,000,000 |

| Typical Gates                         | 82,000   | 154,000  | 286,000  | 612,000       | 1,060,000 |

| Modules                               |          |          |          |               |           |

| Register (R-cells)                    | 672      | 1,408    | 2,688    | 6,048         | 10,752    |

| Combinatorial (C-cells)               | 1,344    | 2,816    | 5,376    | 12,096        | 21,504    |

| Maximum Flip-Flops                    | 1,344    | 2,816    | 5,376    | 12,096        | 21,504    |

| Embedded RAM/FIFO                     |          |          |          |               |           |

| Number of Core RAM Blocks             | 4        | 12       | 16       | 36            | 64        |

| Total Bits of Core RAM                | 18,432   | 55,296   | 73,728   | 165,888       | 294,912   |

| Clocks (Segmentable)                  |          |          |          |               |           |

| Hardwired                             | 4        | 4        | 4        | 4             | 4         |

| Routed                                | 4        | 4        | 4        | 4             | 4         |

| PLLs                                  | 8        | 8        | 8        | 8             | 8         |

| I/Os                                  |          |          |          |               |           |

| I/O Banks                             | 8        | 8        | 8        | 8             | 8         |

| Maximum User I/Os                     | 168      | 248      | 336      | 516           | 684       |

| Maximum LVDS Channels                 | 84       | 124      | 168      | 258           | 342       |

| Total I/O Registers                   | 504      | 744      | 1,008    | 1,548         | 2,052     |

| Package                               |          |          |          |               |           |

| CSP                                   | 180      |          |          |               |           |

| PQFP                                  |          | 208      | 208      |               |           |

| BGA                                   |          |          |          | 729           |           |

| FBGA                                  | 256, 324 | 256, 484 | 484, 676 | 484, 676, 896 | 896, 1152 |

| CQFP                                  | ,        | 208, 352 | 208, 352 | 352           | 352       |

| CCGA                                  |          |          | ,        | 624           | 624       |

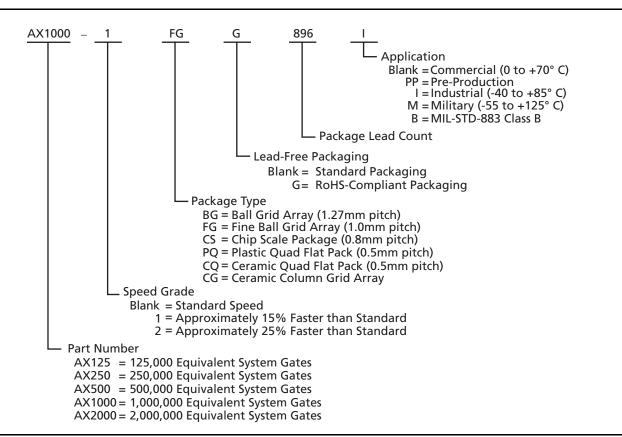

## **Ordering Information**

#### **Device Resources**

| User I/Os (Including Clock Buffers) |       |       |       |        |        |

|-------------------------------------|-------|-------|-------|--------|--------|

| Package                             | AX125 | AX250 | AX500 | AX1000 | AX2000 |

| CS180                               | 98    | _     | _     | _      | _      |

| PQ208                               | _     | 115   | 115   | _      | _      |

| CQ208                               | -     | 115   | 115   | -      | -      |

| FG256                               | 138   | 138   | _     | -      | -      |

| FG324                               | 168   | _     | _     | _      | _      |

| CQ352                               | -     | 198   | 198   | 198    | 198    |

| FG484                               | -     | 248   | 317   | 317    | -      |

| CG624                               | -     | _     | _     | 418    | 418    |

| FG676                               | -     | _     | 336   | 418    | _      |

| BG729                               | -     | -     | _     | 516    | -      |

| FG896                               | -     | _     | _     | 516    | 586    |

| FG1152                              | -     | _     | _     | -      | 684    |

*Note:* The FG256, FG324, and FG484 are footprint compatible with one another. The FG676, FG896, and FG1152 are also footprint compatible with one another.

## **Temperature Grade Offerings**

| Package | AX125 | AX250   | AX500   | AX1000  | AX2000  |

|---------|-------|---------|---------|---------|---------|

| CS180   | C, I  | -       | _       | -       | _       |

| PQ208   | -     | C, I, M | C, I, M | -       | _       |

| CQ208   | -     | M, B    | M, B    | -       | _       |

| FG256   | C, I  | C, I, M | _       | -       | _       |

| FG324   | C, I  | -       | _       | -       | _       |

| CQ352   | -     | M, B    | M, B    | M, B    | М, В    |

| FG484   | -     | C, I, M | C, I, M | C, I, M | _       |

| CG624   | -     | -       | _       | M, B    | М, В    |

| FG676   | -     | -       | C, I, M | C, I, M | _       |

| BG729   | -     | -       | _       | C, I, M | _       |

| FG896   | -     | -       | _       | C, I, M | C, I, M |

| FG1152  | -     | -       | _       | -       | C, I, M |

#### Notes:

1. C = Commercial

2. I = Industrial

3. M = Military

4. B = MIL-STD-883 Class B

## Speed Grade and Temperature Grade Matrix

|   | Std          | -1 | -2 |

|---|--------------|----|----|

| С | 1            | ✓  | ✓  |

|   | $\checkmark$ | ✓  | ✓  |

| М | $\checkmark$ | ✓  | -  |

| В | ✓            | ✓  | _  |

#### Notes:

6. I = Industrial

7. M = Military

8. B = MIL-STD-883 Class B

Contact your local Actel representative for device availability.

<sup>5.</sup> C = Commercial

## **General Description**

Actel's newest FPGA family, Axcelerator offers high performance at densities of up to two million equivalent system gates. Based upon Actel's new AX architecture, Axcelerator has several system level features such as embedded SRAM (with complete FIFO control logic), PLLs, Segmentable Clocks, and chip-wide highway routing.

### **Device Architecture**

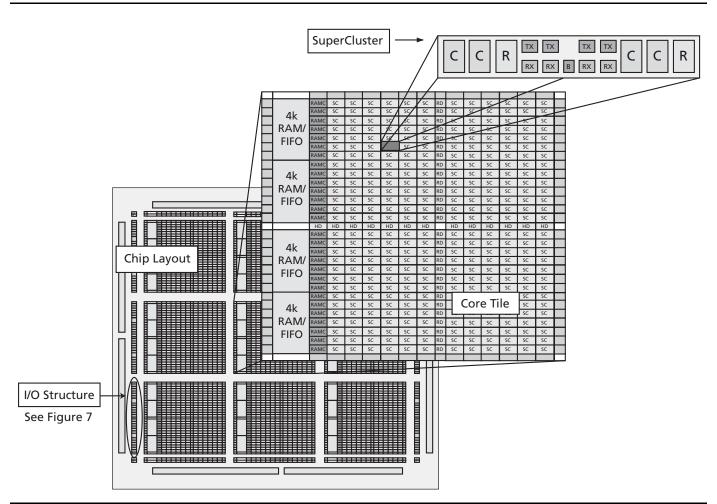

Actel's AX architecture, derived from the highly successful SX-A sea-of-modules architecture, has been designed for high performance and total logic module utilization (Figure 1). There are two base logic modules: the Register Cell (R-cell), containing a full-featured flip-

flop and the Combinatorial Cell (C-cell), containing a four-input MUX with control and carry-chain logic.

Two C-cells and a single R-cell form a Cluster, and two Clusters comprise a SuperCluster. SuperClusters are organized into Core Tiles, which are combined to generate each device (please refer to the Axcelerator Family FPGAs data sheet for more information).

Additionally, each SuperCluster contains an independent Buffer Module. Buffer Modules support automatic buffer insertion for high-fanout nets by the place-and-route tool, providing better overall system delays while improving logic utilization.

The AX architecture is fully fracturable, meaning that if one or more of the logic modules in a SuperCluster are used by a particular signal path, the other logic modules are still available for use by other paths.

Figure 1 • AX Device SuperCluster

### **Embedded Memory**

The embedded, variable-aspect-ratio SRAM blocks have separate read and write ports that can be configured with different bit widths on each port. Available memory configurations are: 128x36, 256x18, 512x9, 1kx4, 2kx2 or 4kx1 bit. Additionally, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO, with programmable DEPTH and programmable ALMOSTEMPTY and ALMOST-FULL flags in addition to the normal FULL and EMPTY flags.

The embedded FIFO control unit also contains the counters necessary for the generation of the read and write address pointers as well as metastable control circuitry to prevent erroneous operation. The metastable control circuitry, when combined with the FIFO's ability for asynchronous reads and writes, enables these embedded structures to be used to cross both clock and phase domains.

#### l/Os

The Axcelerator family of FPGAs also features a flexible I/O structure, supporting a range of mixed voltages with its bank-selectable I/O: 1.5V, 1.8V, 2.5V and 3.3V. In total, Axcelerator FPGAs support at least 14 different I/O standards (single-ended, differential, voltage-referenced).

The I/Os are organized into banks, with eight banks per device (two per side). All I/O options are 3.3V tolerant; the 3.3V PCI option is 5V tolerant with the aid of an external resistor. All I/O options except 3.3V PCI are hot-insertion capable.

Each I/O has an input, output, and enable register.

#### Routing

Tying all of the device resources together is the AX hierarchical routing structure, enabling the Axcelerator family's high performance and utilization. At the lowest level in and SuperClusters below, there are three routing structures: DirectConnects, FastConnects, and CarryConnects. DirectConnects provide very high performance routing inside the SuperCluster, while FastConnects provide high performance routing inside the SuperCluster and to the below SuperCluster.

CarryConnect routing is used between SuperClusters when building arithmetic functions. The core tile routing is at the next level. Both vertical and horizontal tracks run across a row or column of SuperClusters within a core tile respectively. At the chip level, routing highways extend across the full length of the device, both northto- south and east-to-west.

#### **Global Resources**

Each family member has three types of global signals available to the designer: HCLK, CLK, and GCLR/GPSET. There are four hardwired clocks (HCLKs) per device, which can directly drive the clock input of an R-Cell. Each of the four routed clocks (CLKs) can drive the clock, clear, preset, or enable pin of an R-cell or any input of a C-cell. Global clear (GCLR) and global preset (GPSET) can drive the clear and preset inputs of each R-Cell as well as each I/O Register on a chip-wide basis at power up.

Each HCLK and CLK has an associated analog PLL for a total of eight per chip. Each embedded PLL can be used for clock delay minimization, clock delay adjustment, or clock frequency synthesis. The PLL can operate with input frequencies ranging from 14 MHz to 200 MHz and can generate output frequencies between 20 MHz and 1 GHz. The clock can be either divided or multiplied by up to a factor of 64, or multiply and divide settings can be in any combination as long as the resulting clock does not exceed the absolute maximum output value (1 GHz).

Additionally, the PLL can be used to introduce either a positive or a negative clock delay of up to 3.75 ns in 250 ps increments. The reference clock needed to drive the PLL can be derived from three sources: an external input pad (configured as either single-ended or differential), internal logic, or from the output of an adjacent PLL.

#### Summary

Actel's Axcelerator family of FPGAs expands the successful SX-A architecture, adding embedded RAM/ FIFOs, PLLs, and high-speed I/Os. The Axcelerator family also provides the designer with high-performance at high-gate counts with high device utilization even with fixed pins. With the support of a suite of robust software tools, design engineers can incorporate high gate counts and fixed pins into an Axcelerator design yet still achieve high performance and efficient device utilization.

## **Datasheet Categories**

In order to provide the latest information to designers, some datasheets are published before data has been fully characterized. Datasheets are designated as "Product Brief," "Advanced," "Production," and "Web-only." The definition of these categories are as follows:

## **Product Brief**

The product brief is a summarized version of a advanced datasheet (advanced or production) containing general product information. This brief gives an overview of specific device and family information.

### Advanced

This datasheet version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production.

#### **Datasheet Supplement**

The datasheet supplement gives specific device information for a derivative family that differs from the general family datasheet. The supplement is to be used in conjunction with the datasheet to obtain more detailed information and for specifications that do not differ between the two families.

### **Unmarked (production)**

This datasheet version contains information that is considered to be final.

Actel and the Actel logo are registered trademarks of Actel Corporation. All other trademarks are the property of their owners.

## www.actel.com

#### **Actel Corporation**

#### Actel Europe Ltd.

2061 Stierlin Court Mountain View, CA 94043-4655 USA **Phone** 650.318.4200 **Fax** 650.318.4600 River Court, Meadows Business Park Station Approach, Blackwater Camberley Surrey GU17 9AB United Kingdom Phone +44 (0) 1276 609 300 Fax +44 (0) 1276 607 540 Actel Japan EXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668 http://jp.actel.com

#### Actel Hong Kong

Room 2107, China Resources Building 26 Harbour Road Wanchai, Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 www.actel.com.cn